Emulation in virtual mode simplifies debug, improves debug accuracy, creates new applications for emulation, and supports multiple concurrent users through remote access. This paper describes the … [Read more...] about Increase Hardware Emulation Productivity with Virtual Mode

Siemens

Modeling ECD with machine learning to improve CMP simulation

CMP simulation is a valuable tool for determining the optimum CMP process to use during chip manufacturing. Large surface topography variations generated after ECD affect the post-CMP surface profile. … [Read more...] about Modeling ECD with machine learning to improve CMP simulation

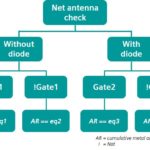

Automated ESD protection verification for 2.5D and 3D ICs

Ensuring your integrated circuit (IC) design has the ability to withstand electrostatic discharge (ESD) events without incurring damage or failure is an extremely important activity in IC circuit … [Read more...] about Automated ESD protection verification for 2.5D and 3D ICs

SoC Verification and Validation on Day 1

Modern electronic systems consist of increasingly complex combinations of hardware and software as a result of continued “digitalization.” Development of these two fundamental aspects of a system tend … [Read more...] about SoC Verification and Validation on Day 1

Automated post-processing of DRC errors improves debugging productivity

Automated post-processing DRC debugging flows enable designers to more quickly and accurately analyze and fix (or waive) a wide range of complex error conditions. By providing designers with more … [Read more...] about Automated post-processing of DRC errors improves debugging productivity

Reliability verification in the cloud delivers significant runtime benefits

Design complexities and time-to-market pressures compel companies to find innovative ways to leverage all available resources. “Not on premises” cloud compute environments provide a scalable and … [Read more...] about Reliability verification in the cloud delivers significant runtime benefits

Calibre AutoWaivers: Automated post-processing of DRC errors improves debugging productivity

Automated post-processing DRC debugging flows enable designers to more quickly and accurately analyze and fix (or waive) a wide range of complex error conditions. By providing designers with more … [Read more...] about Calibre AutoWaivers: Automated post-processing of DRC errors improves debugging productivity

Enabling embedded devices for Industrial Internet of Things (IIoT)

This whitepaper outlines key architectural considerations required for the successful operation of smart devices within an IIoT infrastructure, with a focus on the software that runs on the device … [Read more...] about Enabling embedded devices for Industrial Internet of Things (IIoT)

5G SoCs Demand New Verification Approaches

5G SoC designs must support many use cases, custom configurations, and evolving standards. This means that a colossal amount of testing is required. Designers can no longer create fronthaul hardware … [Read more...] about 5G SoCs Demand New Verification Approaches

Electrical design and wire harness engineering

Electrical systems are constantly growing, whether in passenger cars, aircraft or heavy machinery. The growing size and complexity of these systems is driving up development costs and the likelihood … [Read more...] about Electrical design and wire harness engineering